The Processor

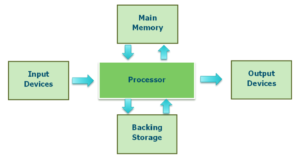

The processor is responsible for carrying out the fetch/execute cycle. This involves accessing memory locations to read and write data, either before or after execution by the processor.

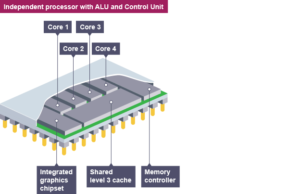

Modern processors are commonly quad core processors. This means that there are actually four processors that make up the central processing unit. At first there was generally only one core on a processor. This evolved to become dual-core (two processors) and now quad-core.

The more processors present, the greater the number of tasks that can be processed simultaneously. This is known as parallel processing, as two different processors can process different tasks (threads) at the same time.

Arithmetic and Logic Unit (ALU)

The Arithmetic and Logic Unit is used by the processor to carry out operations that require the use of:

- Logical operations such as AND, OR, NOT

- Arithmetic operations such as +, -, *, /

Registers

These are very fast temporary storage locations inside the processor which hold:

- data being processed

- instructions being executed

- addresses of memory locations to be accessed

Instruction Register (IR)

Holds the instruction currently being decoded and executed by the processor

The Accumulator (A)

Is a data register which holds the accumulated results of calculations performed in the ALU

The program Counter (PC)

Is a register which holds the address of the main memory location storing the next instruction to be executed

Buses

A bus is a collection of wires through which data is transmitted from one part of a computer to another.

Address Bus

The address bus is uni-directional, meaning that it is concerned with passing an address one way, from the CPU to RAM. The sole purpose of an address bus is to identify the address of the location in cache or main memory that is to be read from or written to. Each location in memory will have its own unique address, this is known as addressability.

Data Bus

The data bus is bi-directional because it can carry data to main memory from the processor and vice versa. The data bus will transfer data to/from the address that is held on the address bus.

The amount of data that can be carried by the data bus depends on the word size. Word size describes the width of the data bus. At the moment new processors will usually have a word size of 64 lines, allowing for 264 bits to be transferred during each cycle.

Control bus

The control bus is used to identify and initiate the instruction to be carried out.

It is not really a bus at all as each line on the bus is used discretely. Some of the common lines in the control bus are:

- Read

- Write

- Clock

- Interrupt

- Reset

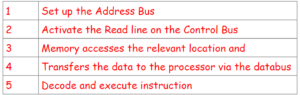

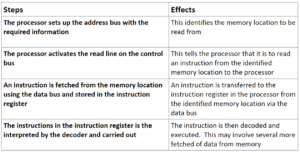

Fetch and Execute Cycle

A program may contain thousands of instructions but the processor can only execute one instruction at a time. The first instruction is fetched from memory in to the processor where it is decoded and executed. Then the second instruction is fetched and then executed and so on until the program ends.

This is known as the FETCH – EXECUTE CYCLE.